# Graphene Nano-Ribbon Field Effect Transistor under Different Ambient Temperatures

M. Akbari Eshkalak\*(C.A.)

**Abstract:** This paper is the first study on the impact of ambient temperature on the electrical characteristics and high frequency performances of double gate armchair graphene nanoribbon field effect transistor (GNRFET). The results illustrate that the GNRFET under high temperature (HT-GNRFET) has the highest cut-off frequency, lowest sub-threshold swing, lowest intrinsic delay and power delay product compared with low-temperature GNRFET (LT-GNRFET) and medium-temperature GNRFET (MT-GNRFET). Besides, the LT-GNRFET demonstrates the lowest off-state current and the highest ratios of lon/loff, average velocity and mobile charge. In addition, the LT-GNRFET has the highest gate and quantum capacitances among three aforementioned GNRFETs.

**Keywords:** GNRFET; Ambient Temperature; Non-Equilibrium Green's Function (NEGF); High Frequency; Two-Dimensional FET Model.

## 1 Introduction

Graphene, a single atomic layer of graphite, is a huge material that experiences a new path in electronic applications. Due to its high carrier mobility and ultrathin body, graphene has attracted significant attention as a material for next-generation technologies that enhance the future high-speed Nano-electronic devices [1, 2].

Graphene is a tremendous candidate as a channel material for future high-speed field effect transistor (FET) performance beyond dimensional scaling. The band-gap of this material is zero. Nevertheless, when patterned into Nano-scale ribbons, a band-gap opens due to the lateral quantum confinement. The narrow stripes of graphene with width less than 100 nm, known as graphene Nano-ribbons (GNRs) have finite energy gaps. The GNRs display an impressive current-carrying capacity of more than 10<sup>8</sup> A/cm2 for the widths down to 16 nm. Furthermore, the breakdown voltage (BV) is estimated to be around 2.5 V for GNRs with widths of 22 nm [3-6].

The GNRs are used as the channel material on the transistors. Transistors made of GNRs are called Graphene-Nano-Ribbon Field Effect Transistors (GNRFETs), which are as potential alternatives to CMOS devices both experimentally and theoretically. One of the critical issues related to transistors is the ratio of ON-state current to OFF-state current ( $I_{on}/I_{off}$ ) which is important parameter on switching

performances of the device. Much of the attention has recently shifted to the use of graphene in RF transistors with large cut-off frequencies ( $f_T$ ) [7-9].

Temperature is one of the device parameter with a major effect on the performance of GNRFET. In this paper we investigate the temperature effects on the electrical behaviour of GNRFET. The simulations are performed based on self-consistent solution of the Poisson- Schrödinger equations coupled with the Non-Equilibrium Green's Function (NEGF) method in mode space representation assuming the tight-binding Hamiltonian. Furthermore, we use a two dimensional "top-of-the-barrier" approach under ballistic transport in our study to extract some of the high-frequency characteristics of the GNRFET. All of the simulations are done under ballistic transport without any scattering and edge effects [10-12].

We have compared the performances of the lowtemperature GNRFET (LT-GNRFET), mediumtemperature GNRFET (MT-GNRFET) and the hightemperature GNRFET (HT-GNRFET). The results show that LT-GNRFET provides the high ratio of  $I_{on}/I_{off}$ which leads to the good switching performance of the device. Furthermore, the HT-GNRFET illustrates the better cut-off frequency and lower intrinsic delay and power delay product (PDP) in comparison with LT-GNRFET and MT-GNRFET.

## 2 Simulation and Modelling

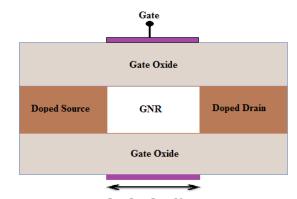

Fig. 1 shows the representation of dual-gated GNRFET under study. A single layer of armchair Graphene Nano-Ribbon (A-GNR) with index of n = 12 is used as the channel material which is taken to be intrinsic. The index n, defines the number of dimmer

Iranian Journal of Electrical & Electronic Engineering, 2016.

Paper received 10 January 2016 and accepted 22 May 2016.

<sup>\*</sup> The Author is with the Department of Electrical Engineering, Roudsar and Amlash Branch, Islamic Azad University, Roudsar, Iran. Email: Mde.Akbari@gmail.com.

carbon atom lines transverse to transport direction which is determined by the GNR width, W. The width and length of this GNR channel are assumed to be W =1.35 nm and L = 12 nm, respectively. The insulating layers have 1 nm thickness and consist of the Sio<sub>2</sub> material with the dielectric constant of K = 3.9. The source and drain regions are assumed to be heavily doped GNR with doping concentration value of  $N_{\rm D} =$ 2.86 ×10<sup>8</sup> m<sup>-1</sup>.

The device characteristics are simulated by solving the ballistic transport equation using the Non-Equilibrium Green's Function (NEGF) formalism selfconsistently with a 2-D Poisson's equation [13, 14]. In NEGF formalism the retarded Green's function of the device is defined as [8, 15],

$$G(E) = \left[ (E + i0^{+})I - H - U - \sum_{s} - \sum_{D} \right]^{-1}$$

(1)

where *H* is the device Hamiltonian. *I* is the identity matrix.  $U = e\phi$  is on-site potential energy, where  $\phi$  is the electrostatic potential which is obtained by solving 2-D Poisson equation.  $\Sigma_{\rm S}$  and  $\Sigma_{\rm D}$  are the self-energies of the source and drain, respectively.

The transmission probability of the carriers is [8],

$$T(E) = trace\left(\Gamma_{s}G\Gamma_{D}G^{+}\right)$$

(2)

where  $\Gamma$  is the contact broadening function extracted as [8],

$$\Gamma_{S(D)} = i(\sum_{S(D)} - \sum_{S(D)}^{+})$$

(3)

Ls = LD = LG = 12 nmFig. 1 Armchair GNRFET under study.

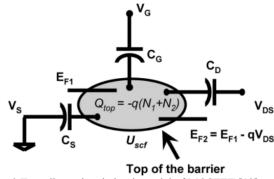

Fig. 2 Two-dimensional circuit model of MOSFET [12].

The local density are calculated using [8],

$$D_{S(D)} = G\Gamma_{S(D)}G^+ \tag{4}$$

The current-voltage characteristic is obtained as follows,

$$I = \frac{2q}{h} \int_{-\infty}^{+\infty} dE T(E) \left\{ f(E, \mu_s) - f(E, \mu_D) \right\}$$

(5)

We have used a capacitance two-dimensional circuit model named "Top-of-the-barrier" model. It is an attempt to extract some of important characteristics of GNRFETs such as velocity, quantum and gate capacitances, mobile charge, intrinsic delay time, power delay product (PDP) and intrinsic cut-off frequency [12, 16].

In this model, the Poisson's equation is solved at the top of the barrier through a capacitance model involving the gate insulator capacitance ( $C_{\rm G}$ ), drain capacitance ( $C_{\rm D}$ ), and source capacitance ( $C_{\rm S}$ ). The aforementioned capacitive model is illustrated in Fig. 2. The potential at the top of the barrier ( $U_{\rm scf}$ ) is controlled by the gate, source and drain potentials and by the location of two Fermi levels  $E_{f1}$  and  $E_{f2}$  [12, 16].

In the shaded region in Fig. 2, the amount of induced mobile charge at the top of the barrier is [12]:

$$Q_{top} = -q\left(N_1 + N_2\right) \tag{6}$$

where  $N_1$  and  $N_2$  are the density of positive velocity states filled by the source and the density of negative velocity states filled by the drain, respectively.

When the terminal biases are zero, the equilibrium electron density at the top of the barrier is  $N_0$ .

$$N_{0} = \int_{-\infty}^{\infty} D(E) f(E - E_{f}) dE$$

(7)

$$N_{1} = \frac{1}{2} \int_{-\infty}^{+\infty} D\left(E - U_{scf}\right) f\left(E - E_{f_{1}}\right) dE$$

(8)

$$N_{2} = \frac{1}{2} \int_{-\infty}^{+\infty} D(E - U_{scf}) f(E - E_{f_{2}}) dE$$

<sup>(9)</sup>

where D(E) is the density of states at the top of the barrier,  $U_{scf}$  is the self-consistent voltage at the top of the barrier,  $E_f$  is the Fermi level and f is the equilibrium Fermi function.  $E_{f1}=E_f$  and  $E_{f2}=E_f - qV_{DS}$  are source and drain Fermi levels respectively.

The expression of the total potential

$$U_{scf}$$

becomes:

$U_{scf} = U_L + U_P$  (10)

where  $U_{\rm L}$  is the Laplace potential and  $U_{\rm P}$  is calculated using the linearized Poisson equation.

The equations of

$$U_{\rm L}$$

and  $U_{\rm P}$  are as follows:

$$U_{L} = -q \left( \alpha_{G} V_{G} + \alpha_{D} V_{D} + \alpha_{S} V_{S} \right)$$

(11)

$$U_{P} = \frac{q^{2}}{C} \Delta N \tag{12}$$

where  $\Delta N = (N_1+N_2)-N_0$  is the biased induced charge at the top of the barrier.

$$\alpha_G = \frac{C_G}{C_{\Sigma}}, \alpha_D = \frac{C_D}{C_{\Sigma}}, \alpha_S = \frac{C_S}{C_{\Sigma}}$$

(13)

where  $C_{\Sigma}$  is the parallel combination of the three capacitors shown in Fig. 2.

The current is given according to the following formula (14):  $I_{\text{DS}}$

$$= \int_{-\infty}^{\infty} J(E - U_{scf}) \Big[ f(E - E_{f_1}) - f(E - E_{f_2}) \Big] dE$$

(14)

where  $J(E-U_{scf})$  is the "current density of states" which is expressed as:  $J(E - U_{scf})$

$$= \frac{1}{2}q \left(\frac{2}{\pi} \sqrt{\frac{2(E-U_{scf})}{m^*}}\right) D(E-U_{scf})$$

(15)

#### **3** Results and Discussions

In this section, the simulation results are presented along with the physical expressions. We study the performance of GNRFET under Three different ambient temperatures of T=200, 300 and 400 K. The GNRFET under the 200 $^{\circ}$ K, 300 $^{\circ}$ K and 400 $^{\circ}$ K temperatures are called LT-GNRFET, MT-GNRFET and HT-GNRFET respectively.

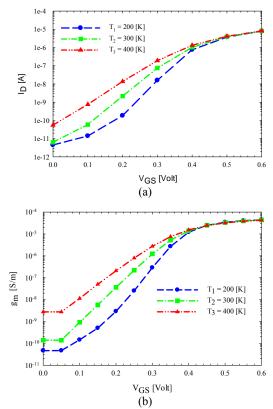

Figs. 3(a) and 3(b) illustrate the simulated IDS-VGS characteristics and transconductance of the GNRFETs under three ambient temperature, respectively. As shown, LT-GNRFET has the lowest Off-state current and transconductance that are good features. This is due to the more thermal emission current stemming from strong control of the gate voltage on the channel near to source.

The transconductance is the ratio of current variation to the gate voltage variation at On-state and is given by [17]:

$$g_m = \frac{\partial I_D}{\partial V_G} \tag{16}$$

Fig. 4(a) depicts the Ion/Ioff ratio for GNRFET under different ambient temperatures. As it shown, the LT-GNRFET has the highest ratio of Ion/Ioff. The reason of this behaviour is described in the Fig. 3(a) where the LT-GNRFET experience the lowest Off-state current.

Fig. 4(b) represents the Sub-threshold Swing (SS) that is a key parameter to transistor miniaturization. Sub-threshold swing value at room temperature is defined with (17) in sub-threshold regime. A device with lower sub-threshold swing is more reliable. The smaller values of SS are desirable for low threshold voltage and low power operation when FETs scaled down to small sizes [18].

$$SS = \frac{dV_G}{d(\log(I_D))}$$

(17)

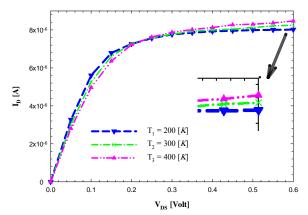

The calculated  $I_{DS}$ - $V_{DS}$  characteristics of the aforementioned GNRFETs are plotted in Fig. 5. We see that the HT-GNRFET has the highest delivering capability due to increase of thermal emission current in comparison with others.

**Fig. 3** (a)  $I_{\rm D}$ - $V_{\rm GS}$  characteristic (b) Transconductance versus the gate voltage for LT-GNRFET, MT-GNRFET and HT-GNRFET at  $V_{\rm DS}$  = 0.6 V.

**Fig. 4** (a)  $I_{on}/I_{off}$  ratio (b) Sub-threshold Swing (SS) versus the temperature for GNRFETs.

**Fig. 5** Simulated current  $I_{DS}$  versus  $V_{DS}$  for GNRFETs under three different ambient temperatures.

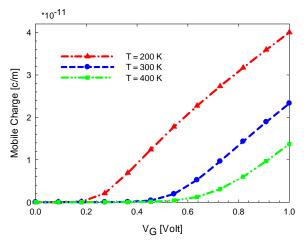

Mobile charge is one of the important figures of merit for the transistors. Fig. 6 shows the variations of the mobile charge as a function of gate-source voltage for GNRFET under three different temperatures. The LT-GNRFET offers the highest mobile charge due to the strong effects of the gate voltage on the channel regions.

Now we discuss the average velocity behavior of carrier at the top of the barrier. This velocity is extracted in the linear region of sample FETs that is defined with [19],

$$\langle v \rangle = \frac{I_D(V_{GS}, V_{DS})}{-q[N_S(V_{GS}, V_{DS}) + N_D(V_{GS}, V_{DS})]}$$

(18)

Fig. 7 illustrates the average electron velocity at top of the barrier versus gate bias for aforementioned GNRFETs. As can be seen, the average electron velocity has the highest ratio for the LT-GNRFET and increases with  $V_{DS}$ .

Fig. 6 Mobile charges versus gate voltage for LT-GNRFET, MT-GNRFET and HT-GNRFET at  $V_{DS} = 0.6$  V.

**Fig. 7** Average electron velocity versus gate voltage for GNRFET under different ambient temperatures.

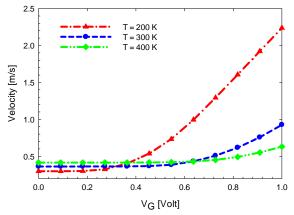

Now, we study the Gate and Quantum capacitances behaviours for GNRFET under different ambient temperatures. The gate capacitance ( $C_G$ ) is modelled as a series combination of quantum capacitance ( $C_Q$ ) and the insulator capacitance ( $C_{ins}$ ) [8],

$$C_G = \frac{C_{i_{ns}}C_Q}{C_{i_{ns}} + C_Q} \tag{19}$$

where the quantum and gate-insulator capacitances are as follows,

$$C_{Q} = \frac{d(qN)}{d(-U_{scf}/q)} = q^{2} \int_{-\infty}^{+\infty} D(E) \left(-\frac{\partial f(E-E_{F})}{\partial E}\right) dE \quad (20)$$

$$C_{ins} = N_G K \varepsilon_0 \left( \frac{W}{t_{ins}} + \alpha \right)$$

(21)

$N_{\rm G}$  is the number of gates, *K* is the relative dielectric constant of gate insulator,  $t_{\rm ins}$  is the insulator thickness and  $\alpha$  is a dimensionless fitting parameter.

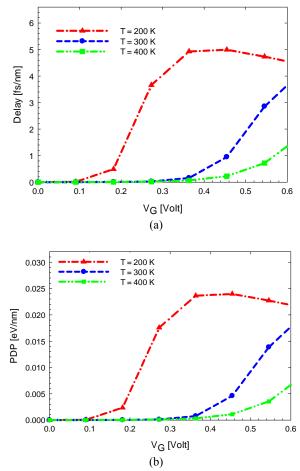

The Gate and Quantum capacitance as a function of gate voltage are shown in Figs. 8(a) and 8(b) respectively. We observe that the LT-GNRFET provides the highest gate capacitance which is a capacitance between gate and the channel region. And the HT-GNRFET offers the lowest quantum capacitance which is especially important for low-density-of-states systems.

When the gate voltage is high, the barrier height between the source and drain decreases, which increases the electron density in the channel, therefore the quantum capacitance increases.

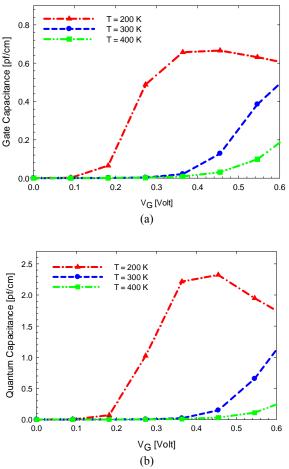

Two important performance metrics that characterize the limitations on AC operation and switching behaviours of a transistor are intrinsic delay time ( $\tau_s$ ) and power-delay product (PDP). The PDP indicates the amount of energy consumed per switching event of the device. The values of intrinsic delay time and PDP can be obtained from Eqs. (22) and (23), respectively [20, 21].

**Fig. 8** (a) Gate capacitance, (b) Quantum capacitance versus gate bias for GNRFET under different ambient temperatures.

$$\tau_s = \frac{C_G V_{DD}}{I_{ON}} \tag{22}$$

$$PDP = (I_{ON}V_{DD})\tau_s \tag{23}$$

where the On-state current is the drain current at  $V_{\rm G} = V_{\rm DD} = V_{\rm DD} = 0.6$  V.

For GNRFETs operating at a given bias condition in linear or saturation regions, the intrinsic delay and PDP can be reduced by improving the material quality and using a better substrate. Here we examine the effects of ambient temperature on the performances of these parameters.

Figs. 9(a) and 9(b) illustrate the variations of switching delay time and PDP versus gate voltage for three aforementioned GNRFETs. We observe that the HT-GNRFET gives the lowest intrinsic delay time and PDP among three structures.

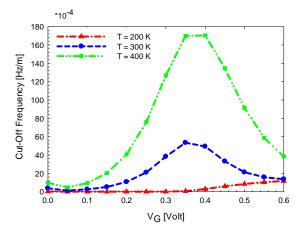

The intrinsic cut-off frequency  $(f_T)$  is an important parameter for high frequency and high speed performances of the transistors. It is the highest frequency, which a FET can support. The value of  $f_T$  can be obtained from the following equation [22],

Fig. 9 (a) Switching delay time (b) Power-delay time product versus the gate voltage for GNRFET under different ambient temperatures.

**Fig. 10** Intrinsic cut-off frequency  $(f_T)$  versus gate bias for GNRFET under different ambient temperatures.

$$f_T = \frac{g_m}{2\pi C_g} \tag{24}$$

151

Fig. 10 presents the variations of the intrinsic cut-off frequency versus the gate bias voltage for GNRFETs under different ambient temperatures. As can be seen, this parameter increases with the gate voltage and sutures then decreases. The HT-GNRFET has the highest amount of  $f_{\rm T}$  which means the best choice among these structures for the radio-frequency applications.

# 4 Conclusion

In this paper, we have studied the effects of different ambient temperatures on performances of Graphene Nano-Ribbon Filed-Effect transistors (GNRFETs). In order to extract the GNRFET characteristics, we applied the Non-Equilibrium Green's Function method to solve the Schrödinger equation self-consistently with 2-D Poisson equation. We have proposed three different ambient temperatures as 200, 300 and 400 kelvin that the GNRFETs with these temperatures are called LT-MT-GNRFET and HT-GNRFET GNRFET, respectively. We have used a double gate GNRFET with 12 nm channel length and source/drain doped reservoir. We have computed the characteristics of the device without the scattering and edge effects. We have investigated the current-voltage characteristics and switching parameters for three aforementioned structures of GNRFET. The results have shown that the LT-GNRFET has the lowest off-state current and the highest ratio of  $I_{on}/I_{off}$  among three aforesaid structures. The GNRFET under low ambient temperature demonstrates the best outputs of transconductance, mobile charge, gate capacitance and average electron velocity. Whereas The HT-GNRFET offers the lowest amount of sub-threshold swing, quantum capacitance, intrinsic delay time and Power delay product. Furthermore, the intrinsic cut-off frequency is calculated. Comparison among the LT-GNRFET, MT-GNRFET and HT-GNRFET revealed that the HT-GNRFET has the highest intrinsic cut-off frequency which is the best structure for the high frequency operations. And the MT-GNRFET offers the middle output characteristics during our discussions.

# References

- S. J. Han, Z. Chen, A. A. Bol, and Y. Sun, "Channel-Length-Dependent Transport Behaviors of Graphene Field-Effect Transistors," *IEEE Electron Device Letters*, Vol. 32, No. 6, pp. 812-814, 2011.

- [2] H. Karimi, R. Yusof, R. Rahmani, H. Hosseinpour, and M. T. Ahmadi, "Development of solutiongated graphene transistor model for biosensors," *Nanoscale Research Letters*, Nano Express, Vol. 9, pp. 1-11, 2014.

- [3] L. A. Openov, and A. I. Podlivaev, "Insulator Band Gap in Graphane Nanoribbons," *Semiconductors*, Vol. 45, No. 5, pp. 633-635, 2011.

- [4] M. Ghadiry, R. Ismail, M. Saeidmanesh, M. Khaledian, and A. Abd Manaf, "Graphene nanoribbon field-effect transistor at high bias," *Nanoscale Research Letters*, Vol. 9, pp. 1-5, 2014.

- [5] H. Owlia, and P. Keshavarzi, "Investigation of the novel attributes of a double-gate graphene nanoribbon FET with AIN high-κ dielectrics," *Superlattices and Microstructures*, Vol. 75, pp. 613-620, 2014.

- [6] M. R. Moslemi, M. H. Sheikhi, K. Saghafi, and M. K. Moravvej-Farshi, "Electronic properties of a dual-gated GNR-FET under uniaxial tensile strain," *Microelectronics Reliability*, Vol. 52, pp. 2579-2584, 2012.

- [7] M. Sanaeepur, A. Yazdanpanah Goharrizi, and M. J. Sharifi, "Performance Analysis of Graphene Nanoribbon Field Effect Transistors in the Presence of Surface Roughness," *IEEE Trans. Electron Devices*, Vol. 61, pp. 1193-1198, 2013.

- [8] M. Akbari Eshkalak, R. Faez, and S. Haji-Nasiri, "A novel graphene nanoribbon field effect transistor with two different gate insulators," *Physica E*, Vol. 66, pp. 133-139, 2015.

- [9] H. Sarvari, R. Ghayour, and E. Dastjerdy, "Frequency analysis of graphene nanoribbon FET by Non-Equilibrium Green"s Function in mode space," *Physica E*, Vol. 43, pp. 1509-1513, 2011.

- [10] R. Grassi, A. Gnudi, E. Gnani, S. Reggiani, and G. Baccarani, "Mode Space Approach for Tight Binding Transport Simulation in Graphene Nanoribbon FETs," *IEEE Trans. Nanotechnology*, Vol. 10, pp. 371-378, 2011.

- [11] M. R. Moslemi, M. K. Moravej-Farshi and M. H. Sheikhi, "Improving Ion/Ioff in dual-gate graphene nanoribbon field-effect transistors using local uniaxial tensile strain," *Physica E*, Vol. 68, pp. 143-148, 2015.

- [12] A. Rahman, J. Guo, S. Datta, and M. S. Lundstrom, "Theory of Ballistic Nanotransistors," *IEEE Trans. Electron Devices*, Vol. 50, pp. 1853-1864, 2003.

- [13] S. S. Ghoreishi, K. Saghafi, R. Yousefi, and M. K. Moravvej-Farshi, "Graphene nanoribbon tunnel field effect transistor with lightly doped drain: Numerical simulations," *Superlattices and Microstructures*, Vol. 75, pp. 245-256, 2014.

- [14] S. K. Chin, D. Seah, K. T. Lam, G. S. Samudra, and G. Liang, "Device Physics and Characteristics of Graphene Nanoribbon Tunneling FETs," *IEEE Trans. Electron Devices*, Vol. 57, pp. 3144-3152, 2010.

- [15] H. Mohammadpour, and A. Asgari, "Numerical study of quantum transport in the double-gate graphene nanoribbon field effect transistors," *Physica E*, Vol. 43, pp. 1708-1711, 2011.

- [16] G. Liang, N. Neophytou, D. E. Nikonov, and M. S. Lundstrom, "Performance Projections for Ballistic Graphene Nanoribbon Field-Effect Transistors,"

*IEEE Trans. Electron Devices*, Vol. 54, pp. 677-682, 2007.

- [17] S. Rodriguez, S. Vaziri, A. Smith, S. Frégonèse, M. Ostling, M. C. Lemme, and A. Rusu, "A Comprehensive Graphene FET Model for Circuit Design," *IEEE Trans. Electron Devices*, Vol. 61, pp. 1199-1206, 2014.

- [18] A. Naderi, "Double gate graphene nanoribbon field effect transistor with electrically induced junctions for source and drain regions," *J. Computational Electronics*, Vol. 15, pp. 347-357, 2016.

- [19] Z. Arefinia, and A. A. Orouji, "Investigation of the novel attributes of a carbon nanotube FET with high-k gate dielectrics," *Physica E*, Vol. 40, pp. 3068-3071, 2008.

- [20] H. Wang, A. Hsu, D. Seup Lee, K. Kang Kim, J. Kong and T. Palacios, "Delay Analysis of Graphene Field-Effect Transistors," *IEEE Electron Device Letters*, Vol. 33, pp. 324-326, 2012.

- [21] K. Alam, "Uniaxial Strain Effects on the Performance of a Ballistic Top Gate Graphene Nanoribbon on Insulator Transistor," *IEEE Trans. Nanotechnology*, Vol. 8, pp. 528-534, 2009.

- [22] W. Wang, H. Wang, X. Wang, N. Li, C. Zhu, G. Xiao, X. Yang, L. Zhang, and T. Zhang, "Quantum Transport Simulations of CNTFETs: Performance Assessment and Comparison Study with GNRFETs," *J. Semiconductor Technology and Science*, Vol. 14, pp. 615-624, 2014.

Maedeh Akbari Eshkalak received her M.Sc. degree in Electronic Engineering from Islamic Azad University, Qazvin, Iran, in 2014. Her research interest is Nano-Electronic.